Via Lach ass och bekannt als Via Lach.Fir Client Ufuerderunge ze treffen, der

Circuit Verwaltungsrot via Lach muss verstoppt ginn.No vill Praxis ass den traditionelle Aluminiumstecker-Lachprozess geännert ginn, an d'Siretboard-Uewerfläche-Lötmaske a Stecker sinn mat wäissem Mesh ofgeschloss.Lach.Stabil Produktioun an zouverlässeg Qualitéit.

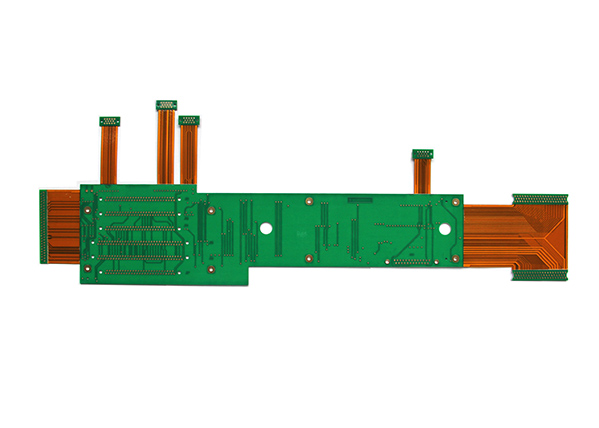

Via Lächer spillen d'Roll vu Verbindungs- a Leedungslinnen.D'Entwécklung vun der Elektronikindustrie fördert och d'Entwécklung vu PCBs, a stellt och méi héich Ufuerderunge fir d'gedréckte Board-Fabrikatiounstechnologie an d'Uewerflächemontéierungstechnologie.Via Lach Plugging Technologie ass entstanen, an déi folgend Ufuerderunge sollten zur selwechter Zäit erfëllt ginn:

(1) Et gëtt nëmmen Kupfer am Via-Lach, an d'Lötmaske kann verstoppt ginn oder net;

(2) Et muss Zinn a Bläi am Via-Lach sinn, mat enger gewësser Dickebedarf (4 Mikron), a kee Solderresist Tënt soll an d'Lach kommen, sou datt Zinnpärelen am Lach verstoppt ginn;

(3) D'Iwwerlächer musse Solderresistenz Tëntstecker Lächer hunn, opak, a däerfen keng Zinnkreesser, Zinnpärelen an Ausgläichbedéngungen hunn.

Firwat musse PCB Circuit Boards vias blockéieren?

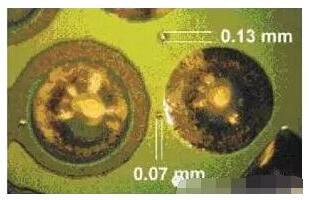

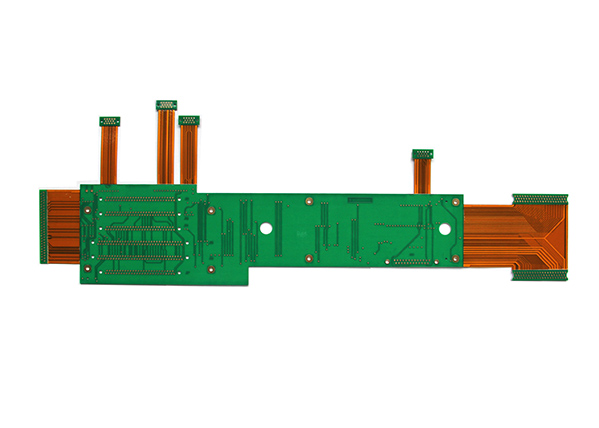

Mat der Entwécklung vun elektronesche Produkter a Richtung "Liicht, dënn, kuerz a kleng", entwéckelen PCBs och Richtung héich Dicht an héich Schwieregkeet.Dofir sinn eng grouss Zuel vu SMT a BGA PCBs erschéngen, a Clienten erfuerderen Plug Lächer beim Montage vun Komponenten, haaptsächlech fënnef Funktiounen abegraff:

(1) Verhënnert datt d'Zinn duerch d'Komponentefläch duerch d'Via-Lach penetréiert fir e Kuerzschluss ze verursaachen, wann de PCB duerch d'Wellesolderung passéiert;virun allem wann mir Plaz der via Lach op der BGA Pad, mir mussen éischt eng Plug Lach maachen, an dann Gold-plated BGA soldering ze erliichteren.

(2) Vermeiden Flux Reschter am via Lach;

(3) Nodeems d'Uewerflächmontage an d'Komponentenmontage vun der Elektronikfabrik ofgeschloss ass, muss de PCB op der Testmaschinn vacuuméiert ginn fir en negativen Drock ze bilden ier se ofgeschloss ass:

(4) Verhënnert datt d'Uewerflächesolderpaste an d'Lach fléisst fir virtuell Schweess ze verursaachen, wat d'Montage beaflosst;

(5) Verhënnert datt d'Zinnpärelen während der Welleléisung erauskommen, wat Kuerzschluss verursaacht.

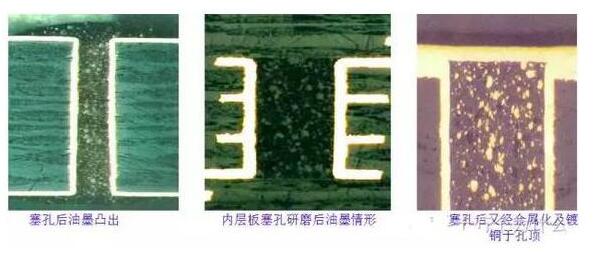

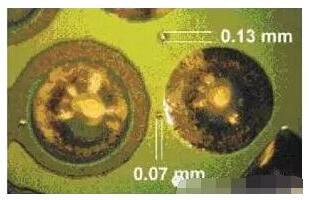

Realisatioun vun Conductive Lach Plugging Technology

Fir Uewerfläch Montéierung Brieder, virun allem fir BGA an IC Opriichte, muss via Lächer flaach ginn, mat engem konvex an konkave plus oder Minus 1 mil, an et däerf kee roude Zinn op de Rand vun der via Lach ginn;Zinnpärelen sinn am Via-Lach verstoppt, fir d'Zefriddenheet vun de Clienten z'erreechen.Et ginn dacks Problemer wéi Ueleg Verloscht während waarm Loft nivellering a gréng Ueleg solder Resistenz Experimenter;Ueleg Explosioun no Aushärtung.Elo no den aktuellen Produktiounsbedingunge sinn déi verschidde Plug-Lachprozesser vu PCB zesummegefaasst, an e puer Vergläicher an Erklärunge ginn am Prozess gemaach, Virdeeler an Nodeeler:

Bemierkung: Den Aarbechtsprinzip vun der Heissluftnivellerung ass waarm Loft ze benotzen fir d'iwwerschësseg Löt op der Uewerfläch vum gedréckte Circuit Board an an de Lächer ze läschen, an de verbleiwen Löt ass gläichméisseg op de Pads, net-Resistenz-Lötleitungen an Uewerfläch bedeckt Verpackungspunkten, dat ass d'Uewerflächenbehandlungsmethod vum gedréckte Circuit Board.eent.

1. Plug Lach Prozess no waarm Loft Niveau

De Prozess Flux ass: Bord Uewerfläch solder Mask → HAL → Plug Lach → Aushärtung.Den Net-Plugging Prozess gëtt fir d'Produktioun benotzt.Nodeems d'waarm Loft ausgeglach ass, gëtt den Aluminiumbildschierm oder den Tëntblockéierungsbildschierm benotzt fir d'Iwwerlochverstoppung vun all de Festungen ze kompletéieren déi vum Client erfuerderlech sinn.D'Verstoppt Tënt kann fotosensibel Tënt oder thermohärtend Tënt sinn.Am Fall vun der selwechter Faarf vum naass Film assuréieren, ass d'Verstoppt Tënt am beschten déiselwecht Tënt wéi d'Brettfläch ze benotzen.Dëse Prozess kann suergen, datt d'via Lach net Ueleg erofléisst nodeems d'waarm Loft ausgeglach ass, awer et ass einfach datt d'Plug Lach Tënt d'Brettfläch kontaminéiert an ongläich ass.Et ass einfach fir Clienten virtuell Solderung ze verursaachen (besonnesch a BGA) beim Montage.Sou vill Clienten akzeptéieren dës Method net.

2. Plug Lach Prozess virun waarm Loft Niveau

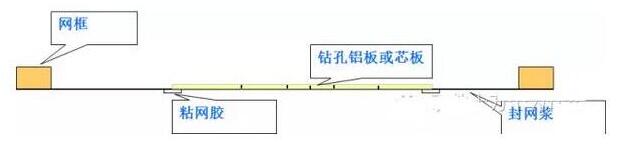

2.1 Benotzt Aluminiumplack fir Lächer ze pluggen, ze heelen an d'Plack fir Mustertransfer ze schleifen

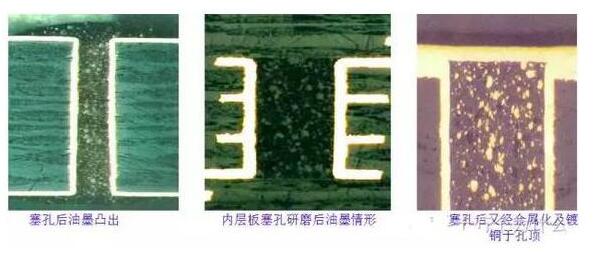

An dësem Prozess gëtt eng CNC Buermaschinn benotzt fir d'Aluminiumplack auszebueren, déi verstoppt muss ginn, eng Bildschirmplack ze maachen, an d'Lächer ze stecken fir sécherzestellen datt d'Via Lächer voll sinn, an d'Steckertënt gëtt benotzt fir d'Lach ze verstoppen ., d'Harz-Schrumpfännerung ass kleng, an d'Verbindungskraaft mat der Lachmauer ass gutt.De Prozessfloss ass: Virbehandlung → Steckerloch → Schleifplack → Mustertransfer → Ätzen → Board Surface Solder Mask

Dës Method kann suergen, datt d'Iwwer-Lach Plug Lach flaach ass, an der waarm Loft nivellering wäert net Qualitéit Problemer wéi Ueleg Explosioun an Ueleg Verloscht um Rand vun der Lach hunn, mä dëse Prozess verlaangt eemol thickening vun Koffer, sou datt d'Kupferdicke vun der Lachmauer kann de Standard vum Client treffen.Dofir sinn d'Ufuerderunge fir d'Kupferplack op der ganzer Plack ganz héich, an et ginn och héich Ufuerderunge fir d'Performance vun der Schleifmaschinn fir sécherzestellen datt d'Harz op der Kupferfläch komplett ewechgeholl gëtt, an d'Kupferfläch ass propper a fräi vu Verschmotzung.Vill PCB Fabriken hunn keen eemolege Verdickungsprozess, an d'Leeschtung vun der Ausrüstung entsprécht net den Ufuerderunge, wat resultéiert datt dëse Prozess net vill an PCB Fabriken benotzt gëtt.

2.2 Nodeems Dir d'Lächer mat Aluminiumplacke verstoppt hutt, screent d'Lötmask direkt op der Boardoberfläche

An dësem Prozess gëtt eng CNC Buermaschinn benotzt fir d'Aluminiumplack auszebueren, déi verstoppt muss ginn fir eng Bildschirmplack ze maachen, déi op der Écrandruckmaschinn installéiert ass fir ze pluggen.Nodeems de Stecker fäerdeg ass, sollt et net méi wéi 30 Minutten geparkt ginn.De Prozessfloss ass: Virbehandlung - Steckerloch - Seidbildschierm - Virbaken - Belaaschtung - Entwécklung - Aushärten

Dëse Prozess kann suergen datt d'Iwwerlaascht gutt mat Ueleg bedeckt ass, d'Plugloch flaach ass, an d'Faarf vum naass Film ass d'selwecht.Pads, wat zu enger schlechter Solderbarkeet resultéiert;no waarm Loft Leveling, de Rand vun der via Lach Bubbles an Ueleg geläscht.Et ass schwéier d'Produktioun mat dëser Prozessmethod ze kontrolléieren, an de Prozessingenieur muss speziell Prozesser a Parameteren adoptéieren fir d'Qualitéit vum Plug Lach ze garantéieren.

Firwat musse PCB Circuit Boards vias blockéieren?

2.3 Nodeems d'Aluminiumplack d'Lächer verstoppt, entwéckelt, pre-kuréiert a schleift d'Brett, gëtt d'Brettoberfläche solderéiert.

Benotzt eng CNC Buermaschinn fir d'Aluminiumplack ze bueren, déi Plug Lächer erfuerdert, e Bildschiermplack maachen an et op enger Verréckelung Écran Dréckmaschinn fir Plug Lächer installéieren.D'Stecker Lächer musse voll sinn, a béid Säite si virun allem eraus.De Prozessfloss ass: Pre-Behandlung - Plug Lach - Pre-Backen - Entwécklung - Pre-curing - Bord Uewerfläch solder Mask

Well dëse Prozess Plug-Lach-Härung adoptéiert fir sécherzestellen datt d'Via-Lach keen Ueleg verléiert oder Ueleg nom HAL explodéiert, awer nom HAL, ass et schwéier de Problem vun Zinnpärelen am Via-Lach an Zinn am Via-Lach komplett ze léisen, sou vill Clienten akzeptéieren et net.

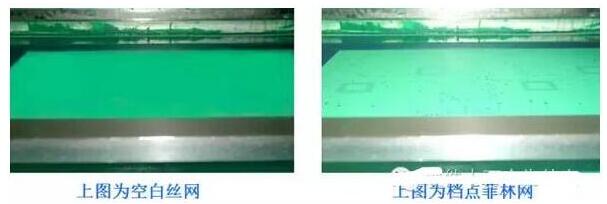

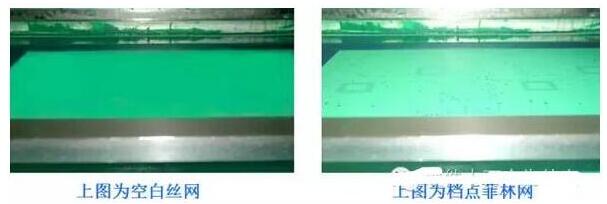

2.4 D'Lötmaske op der Brettfläch an d'Plugloch sinn zur selwechter Zäit fäerdeg.

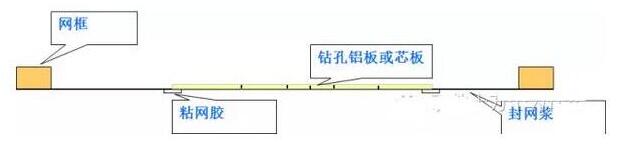

Dës Method benotzt 36T (43T) Écran Mesh gemaach, déi op der Écran Dréckerei Maschinn installéiert ass, mat enger Récksäit Plack oder engem Nol Bett, an plugging all via Lächer iwwerdeems de Bord Uewerfläch komplett.De Prozessfloss ass: Virbehandlung - Écran Dréckerei - Pre-Baken - Beliichtung - Entwécklung - Cure

Dëse Prozess huet eng kuerz Zäit an eng héich Benotzen Taux vun Ausrüstung, déi suergen kann, datt d'via Lächer net Ueleg verléieren an d'Via Lächer gëtt net tinned no waarm Loft nivellering., D'Loft erweidert a brécht duerch d'Soldermaske, wat Leedungen an Ongläichheet verursaacht.Et gëtt eng kleng Quantitéit vun via Lächer an Zinn verstoppt während waarm Loft nivellering.Am Moment huet eis Firma am Fong d'Lach an d'Ongläichheet vum Via Lach no vill Experimenter geléist, verschidden Aarte vun Tënt a Viskositéit auswielen, den Drock vum Seidbilddruck ugepasst, etc., an dëse Prozess gouf fir Masseproduktioun ugeholl. .

English en

English en