PCB EMC डिझाइनची गुरुकिल्ली म्हणजे रीफ्लो क्षेत्र कमी करणे आणि रीफ्लो मार्ग डिझाइनच्या दिशेने वाहू देणे.सर्वात सामान्य रिटर्न वर्तमान समस्या संदर्भ विमानातील क्रॅक, संदर्भ विमान स्तर बदलणे आणि कनेक्टरमधून वाहणारे सिग्नल यामुळे येतात.

जंपर कॅपेसिटर किंवा डिकपलिंग कॅपेसिटर काही समस्या सोडवू शकतात, परंतु कॅपेसिटर, वियास, पॅड आणि वायरिंगचा एकंदर प्रतिबाधा विचारात घेणे आवश्यक आहे.

हा लेख EMC चा परिचय करून देईल पीसीबी डिझाइन तीन पैलूंमधून तंत्रज्ञान: पीसीबी लेयरिंग धोरण, मांडणी कौशल्ये आणि वायरिंग नियम.

पीसीबी लेयरिंग धोरण

सर्किट बोर्ड डिझाइनमधील जाडी, प्रक्रियेद्वारे आणि स्तरांची संख्या ही समस्या सोडवण्याची गुरुकिल्ली नाही.पॉवर बसचे बायपास आणि डीकपलिंग सुनिश्चित करणे आणि पॉवर लेयर किंवा ग्राउंड लेयरवरील क्षणिक व्होल्टेज कमी करणे हे चांगले स्तरित स्टॅकिंग आहे.सिग्नल आणि पॉवर सप्लायच्या इलेक्ट्रोमॅग्नेटिक फील्डचे संरक्षण करण्याची गुरुकिल्ली.

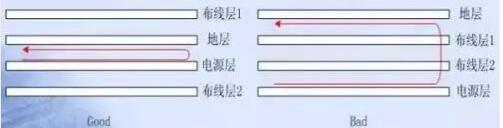

सिग्नल ट्रेसच्या दृष्टीकोनातून, सर्व सिग्नल ट्रेस एक किंवा अनेक स्तरांवर ठेवणे ही एक चांगली लेयरिंग धोरण असावी आणि हे स्तर पॉवर लेयर किंवा ग्राउंड लेयरच्या पुढे असतात.वीज पुरवठ्यासाठी, लेयरिंगची चांगली रणनीती अशी असावी की पॉवर लेयर जमिनीच्या थराला लागून असेल आणि पॉवर लेयर आणि ग्राउंड लेयरमधील अंतर शक्य तितके कमी असेल.हे आम्ही "लेयरिंग" धोरणाबद्दल बोलत आहोत.खाली आम्ही विशेषतः चांगल्या पीसीबी लेयरिंग धोरणाबद्दल बोलू.

1. वायरिंग लेयरचे प्रोजेक्शन प्लेन रिफ्लो प्लेन लेयरच्या क्षेत्रामध्ये असावे.वायरिंग लेयर रिफ्लो प्लेन लेयरच्या प्रोजेक्शन एरियामध्ये नसल्यास, वायरिंग दरम्यान प्रोजेक्शन एरियाच्या बाहेर सिग्नल लाईन्स असतील, ज्यामुळे "एज रेडिएशन" समस्या निर्माण होतील आणि सिग्नल लूपचे क्षेत्र देखील वाढेल, परिणामी वाढीव विभेदक मोड रेडिएशन

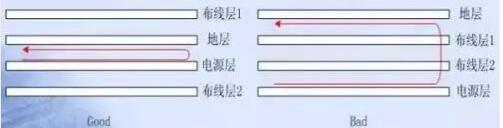

2. समीप वायरिंग स्तर सेट करणे टाळण्याचा प्रयत्न करा.कारण समीप वायरिंग स्तरांवरील समांतर सिग्नल ट्रेस सिग्नल क्रॉसस्टॉकला कारणीभूत ठरू शकतात, जर समीप वायरिंग स्तर टाळता येत नसेल तर, दोन वायरिंग स्तरांमधील लेयर अंतर योग्यरित्या वाढवले पाहिजे आणि वायरिंग लेयर आणि त्याच्या सिग्नल सर्किटमधील लेयर अंतर कमी केले पाहिजे.

3. समीप समतल स्तरांनी त्यांच्या प्रोजेक्शन प्लेनचे ओव्हरलॅपिंग टाळले पाहिजे.कारण जेव्हा प्रक्षेपण ओव्हरलॅप होतात, तेव्हा स्तरांमधील कपलिंग कॅपेसिटन्समुळे थरांमधील आवाज एकमेकांशी जोडला जातो.

मल्टीलेयर बोर्ड डिझाइन

जेव्हा घड्याळाची वारंवारता 5MHz पेक्षा जास्त असते, किंवा सिग्नल वाढण्याची वेळ 5ns पेक्षा कमी असते, तेव्हा सिग्नल लूप क्षेत्र चांगल्या प्रकारे नियंत्रित करण्यासाठी, बहु-स्तर बोर्ड डिझाइनची आवश्यकता असते.मल्टीलेयर बोर्ड डिझाइन करताना खालील तत्त्वांकडे लक्ष दिले पाहिजे:

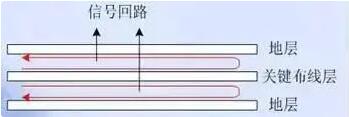

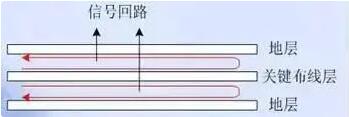

1. की वायरिंग लेयर (ज्या थरात घड्याळाची लाईन, बस, इंटरफेस सिग्नल लाईन, रेडिओ फ्रिक्वेन्सी लाईन, रिसेट सिग्नल लाईन, चिप सिलेक्ट सिग्नल लाईन आणि विविध कंट्रोल सिग्नल लाईन्स असतात) शक्यतो संपूर्ण ग्राउंड प्लेनला लागून असावे. आकृती 1 मध्ये दर्शविल्याप्रमाणे दोन ग्राउंड प्लेन दरम्यान.

की सिग्नल लाईन्स सामान्यतः मजबूत रेडिएशन किंवा अत्यंत संवेदनशील सिग्नल लाईन्स असतात.ग्राउंड प्लेनच्या जवळ वायरिंग केल्याने सिग्नल लूप क्षेत्र कमी होऊ शकते, रेडिएशनची तीव्रता कमी होते किंवा हस्तक्षेप विरोधी क्षमता सुधारते.

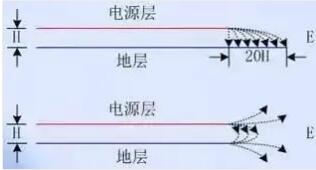

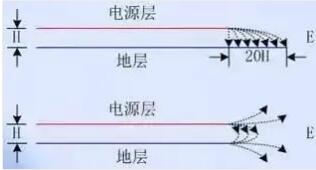

2. पॉवर प्लेन त्याच्या जवळच्या ग्राउंड प्लेनच्या सापेक्ष मागे घेतले पाहिजे (शिफारस केलेले मूल्य 5H~20H).पॉवर प्लेन त्याच्या रिटर्न ग्राउंड प्लेनच्या सापेक्ष मागे घेणे आकृती 2 मध्ये दर्शविल्याप्रमाणे "एज रेडिएशन" समस्या प्रभावीपणे दाबू शकते.

याव्यतिरिक्त, आकृती 3 मध्ये दर्शविल्याप्रमाणे, पॉवर करंटचे लूप क्षेत्र प्रभावीपणे कमी करण्यासाठी बोर्डचे मुख्य कार्यरत पॉवर प्लेन (सर्वाधिक प्रमाणात वापरलेले पॉवर प्लेन) त्याच्या ग्राउंड प्लेनच्या जवळ असले पाहिजे.

3. बोर्डच्या TOP आणि BOTTOM स्तरावर सिग्नल लाइन ≥50MHz नाही.तसे असल्यास, अंतराळातील किरणोत्सर्ग रोखण्यासाठी दोन समतल स्तरांमधील उच्च-फ्रिक्वेंसी सिग्नलवर चालणे चांगले.

सिंगल-लेयर बोर्ड आणि डबल-लेयर बोर्ड डिझाइन

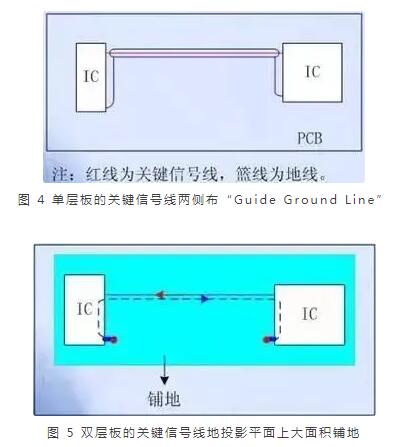

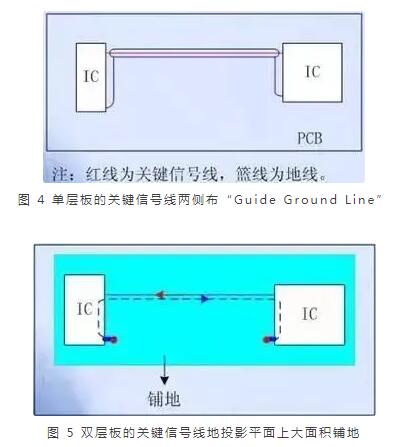

सिंगल-लेयर बोर्ड आणि डबल-लेयर बोर्डच्या डिझाइनसाठी, की सिग्नल लाइन्स आणि पॉवर लाइन्सच्या डिझाइनकडे लक्ष दिले पाहिजे.पॉवर करंट लूपचे क्षेत्रफळ कमी करण्यासाठी पॉवर ट्रेसच्या पुढे आणि समांतर ग्राउंड वायर असणे आवश्यक आहे.

आकृती 4 मध्ये दर्शविल्याप्रमाणे, सिंगल-लेयर बोर्डच्या की सिग्नल लाईनच्या दोन्ही बाजूंना “मार्गदर्शक ग्राउंड लाइन” घातली पाहिजे. दुहेरी-लेयर बोर्डच्या की सिग्नल लाईनमध्ये प्रोजेक्शन प्लेनवर जमिनीचा मोठा भाग असावा. , किंवा सिंगल-लेयर बोर्ड सारखीच पद्धत, आकृती 5 मध्ये दर्शविल्याप्रमाणे "मार्गदर्शक ग्राउंड लाइन" डिझाइन करा. की सिग्नल लाईनच्या दोन्ही बाजूंना "गार्ड ग्राउंड वायर" एकीकडे सिग्नल लूप क्षेत्र कमी करू शकते, आणि सिग्नल लाईन आणि इतर सिग्नल लाईन्समधील क्रॉसस्टॉक देखील प्रतिबंधित करते.

पीसीबी लेआउट कौशल्ये

PCB लेआउट डिझाइन करताना, तुम्ही सिग्नल प्रवाहाच्या दिशेने सरळ रेषेत ठेवण्याचे डिझाइन तत्त्व पूर्णपणे पाळले पाहिजे आणि आकृती 6 मध्ये दर्शविल्याप्रमाणे, मागे व मागे पळणे टाळण्याचा प्रयत्न केला पाहिजे. यामुळे थेट सिग्नल जोडणे टाळता येते आणि सिग्नलच्या गुणवत्तेवर परिणाम होतो. .

याव्यतिरिक्त, सर्किट्स आणि इलेक्ट्रॉनिक घटकांमधील परस्पर हस्तक्षेप आणि कपलिंग टाळण्यासाठी, सर्किट्सची नियुक्ती आणि घटकांचे लेआउट खालील तत्त्वांचे पालन केले पाहिजे:

1. जर बोर्डवर "क्लीन ग्राउंड" इंटरफेस तयार केला असेल, तर फिल्टरिंग आणि आयसोलेशन घटक "स्वच्छ ग्राउंड" आणि वर्किंग ग्राउंड दरम्यान अलगाव बँडवर ठेवले पाहिजेत.हे फिल्टरिंग किंवा अलगाव उपकरणांना प्लानर लेयरद्वारे एकमेकांशी जोडण्यापासून रोखू शकते, ज्यामुळे प्रभाव कमकुवत होतो.याव्यतिरिक्त, "स्वच्छ जमिनीवर" फिल्टरिंग आणि संरक्षण उपकरणांव्यतिरिक्त, इतर कोणतीही साधने ठेवली जाऊ शकत नाहीत.

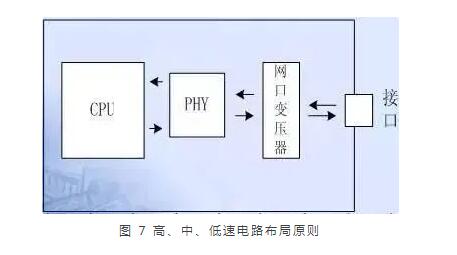

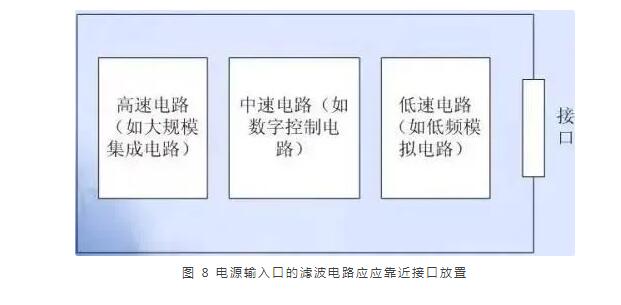

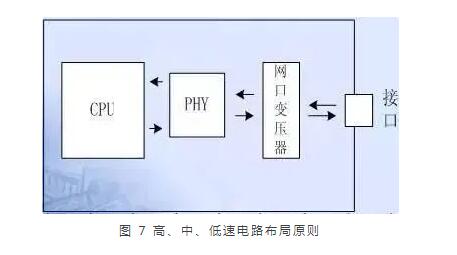

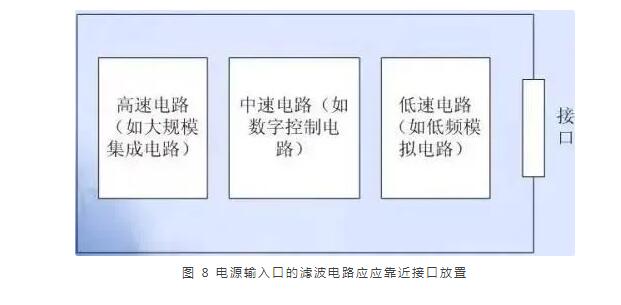

2. जेव्हा एकाच पीसीबीवर एकाधिक मॉड्यूल सर्किट्स ठेवल्या जातात, तेव्हा डिजिटल सर्किट्स आणि अॅनालॉग सर्किट्स, हाय-स्पीड आणि लो-स्पीड सर्किट्स डिजिटल सर्किट्स, अॅनालॉग सर्किट्स, हाय-स्पीड सर्किट्स आणि लो स्पीड सर्किट्समध्ये परस्पर हस्तक्षेप टाळण्यासाठी स्वतंत्रपणे मांडले जावेत. - स्पीड सर्किट्स.याव्यतिरिक्त, जेव्हा सर्किट बोर्डवर उच्च, मध्यम आणि कमी-स्पीड सर्किट्स एकाच वेळी अस्तित्वात असतात, तेव्हा उच्च-फ्रिक्वेंसी सर्किटचा आवाज इंटरफेसमधून बाहेर येऊ नये म्हणून, आकृती 7 मधील मांडणी तत्त्व असावे.

3. फिल्टर केलेले सर्किट पुन्हा जोडणे टाळण्यासाठी सर्किट बोर्डच्या पॉवर इनपुट पोर्टचे फिल्टर सर्किट इंटरफेसच्या जवळ ठेवले पाहिजे.

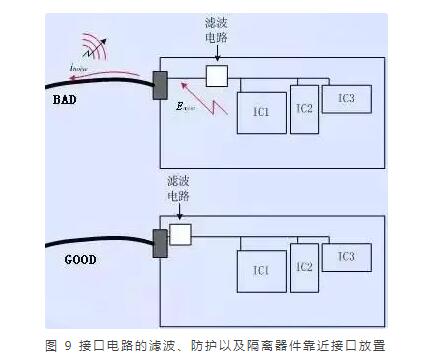

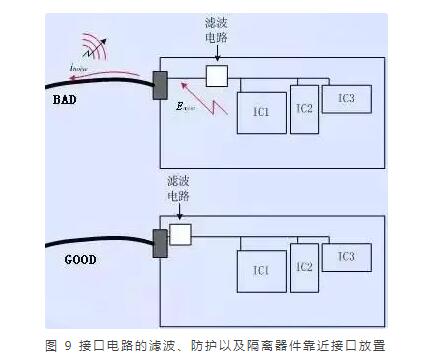

4. आकृती 9 मध्ये दर्शविल्याप्रमाणे इंटरफेस सर्किटचे फिल्टरिंग, संरक्षण आणि अलगाव घटक इंटरफेसच्या जवळ ठेवलेले आहेत, जे संरक्षण, फिल्टरिंग आणि अलगावचे परिणाम प्रभावीपणे साध्य करू शकतात.इंटरफेसमध्ये फिल्टर आणि संरक्षण सर्किट दोन्ही असल्यास, प्रथम संरक्षण आणि नंतर फिल्टरिंगचे तत्त्व असावे.कारण संरक्षण सर्किट बाह्य ओव्हरव्होल्टेज आणि ओव्हरकरंट सप्रेशनसाठी वापरले जाते, जर फिल्टर सर्किट नंतर संरक्षण सर्किट ठेवल्यास, फिल्टर सर्किट ओव्हरव्होल्टेज आणि ओव्हरकरंटमुळे खराब होईल.

याव्यतिरिक्त, सर्किटच्या इनपुट आणि आउटपुट लाइन्स एकमेकांशी जोडल्या गेल्यावर फिल्टरिंग, अलगाव किंवा संरक्षण प्रभाव कमकुवत करतात, याची खात्री करा की फिल्टर सर्किट (फिल्टर), अलगाव आणि संरक्षण सर्किटच्या इनपुट आणि आउटपुट रेषा नाहीत. लेआउट दरम्यान एकमेकांसोबत जोडपे.

5. संवेदनशील सर्किट्स किंवा घटक (जसे की रीसेट सर्किट्स इ.) बोर्डच्या प्रत्येक काठापासून, विशेषतः बोर्ड इंटरफेसच्या काठापासून किमान 1000 मैल दूर असले पाहिजेत.

6. मोठ्या प्रवाहाचे लूप क्षेत्र कमी करण्यासाठी ऊर्जा साठवण आणि उच्च-फ्रिक्वेंसी फिल्टर कॅपेसिटर युनिट सर्किट्स किंवा मोठ्या विद्युत् प्रवाहातील बदलांसह (जसे की वीज पुरवठा मॉड्यूलचे इनपुट आणि आउटपुट टर्मिनल्स, पंखे आणि रिले) उपकरणांजवळ ठेवावे. पळवाट

7. फिल्टर केलेल्या सर्किटला पुन्हा व्यत्यय येण्यापासून रोखण्यासाठी फिल्टरचे घटक बाजूला ठेवावेत.

8. मजबूत रेडिएशन उपकरणे जसे की क्रिस्टल्स, क्रिस्टल ऑसिलेटर, रिले, स्विचिंग पॉवर सप्लाय इ. बोर्ड इंटरफेस कनेक्टरपासून कमीतकमी 1000 मील दूर ठेवा.अशाप्रकारे, हस्तक्षेप थेट बाहेरून रेडिएट केला जाऊ शकतो किंवा विद्युत् प्रवाह बाहेरून विकिरण करण्यासाठी आउटगोइंग केबलशी जोडला जाऊ शकतो.

रियल्टर: मुद्रित सर्किट बोर्ड, पीसीबी डिझाइन, पीसीबी असेंब्ली

English en

English en