RF PCB Verwaltungsrot Layout fir falsch Signaler ze reduzéieren erfuerdert d'Kreativitéit vum RF Ingenieur.Dës aacht Regelen am Kapp ze halen hëlleft net nëmmen d'Zäit op de Maart ze beschleunegen, awer och d'Prévisibilitéit vun Ärem Aarbechtsplang ze erhéijen.

Regel 1: Buedem vias soll um Buedem Referenz Fliger schalt läit All Stréim déi duerch d'routéiert Linn fléissen hunn e gläiche Retour.Et gi vill Kopplungsstrategien, awer de Retourfluss fléisst normalerweis duerch Nopeschbunnen oder Terrainen parallel mat Signallinnen.Wéi d'Referenzschicht weider geet, ass all Kupplung op d'Transmissiounslinn limitéiert an alles funktionnéiert perfekt gutt.Wéi och ëmmer, wann d'Signalrouting vun der ieweschter Schicht op déi bannescht oder ënnen Schicht gewiesselt gëtt, muss de Retourfluss och e Wee kréien.

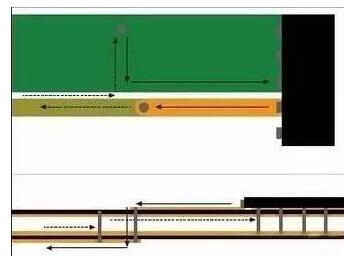

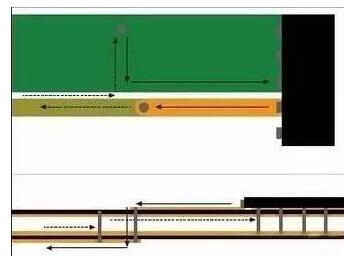

Figur 1 ass e Beispill.Direkt ënner dem Top-Niveau Signallinnstroum ass de Retourfluss.Wann et op déi ënnescht Schicht transferéiert gëtt, geet de Reflow duerch d'nächst Vias.Wéi och ëmmer, wann et keng Vias fir Reflow an der Géigend sinn, geet de Reflow duerch den nooste verfügbare Buedem iwwer.Méi grouss Distanzen kreéieren Stroumschleifen, bilden Induktoren.Wann dës onerwënschten aktuell Wee Offset eng aner Linn iwwerschreift, wäert d'Interferenz méi schwéier sinn.Dës aktuell Loop ass tatsächlech gläichwäerteg mat der Form vun enger Antenne!

Aacht Regele fir Iech ze hëllefen RF PCB Circuit Parasitics ze reduzéieren

Figur 1: Signal Stroum fléisst vun Apparat Pins duerch vias zu ënneschten Schichten.De Reflow ass ënner dem Signal ier se op déi nootste Via gezwongen ass fir op eng aner Referenzschicht z'änneren

Figur 1: Signal Stroum fléisst vun Apparat Pins duerch vias zu ënneschten Schichten.De Reflow ass ënner dem Signal ier se op déi nootste Via gezwongen ass fir op eng aner Referenzschicht z'änneren Buedem Referenz ass déi bescht Strategie, awer Héichgeschwindegkeetslinnen kënnen heiansdo op intern Schichten plazéiert ginn.Buedem Referenz Fligeren uewen an ënnen ze placéieren ass ganz schwéier, an semiconductor Hiersteller vläicht pin-beschränkt a Plaz Muecht Linnen nieft Héich-Vitesse Linnen.Wann de Referenzstroum muss tëscht Schichten oder Netzer gewiesselt ginn, déi net DC-gekoppelt sinn, sollten Ofkopplungskondensatoren nieft dem Schaltpunkt plazéiert ginn.

Regel 2: Connect den Apparat Pad un der ieweschter Schicht Buedem Vill Apparater benotzen en thermesche Buedempad um Enn vum Apparat Package.Op RF-Geräter sinn dës typesch elektresch Terrainen, an ugrenzend Padpunkte hunn eng ganz Rëtsch vu Buedemvias.D'Apparat Pad kann direkt un de Buedem PIN verbonne ginn a verbonne mat all Koffer pour duerch d'Top Layer Buedem.Wann et méi Weeër gëtt, gëtt de Retourfloss proportional zu der Weeimpedanz opgedeelt.D'Buedemverbindung duerch de Pad huet e méi kuerzen a méi nidderegen Impedanzwee wéi de Pin-Buedem.

Eng gutt elektresch Verbindung tëscht dem Board an den Apparatpads ass kritesch.Wärend der Assemblée kënnen net gefëllte Vias an engem Circuitboard iwwer Array och Lötpaste aus dem Apparat erauszéien, an d'Voids hannerloossen.Duerch Lächer ausfëllen ass e gudde Wee fir d'Lötung op der Plaz ze halen.Wärend der Evaluatioun, öffnen och d'Lötmaskschicht fir z'iwwerpréiwen datt et keng Lötmaske um Bordbuedem ënner dem Apparat ass, well d'Lötmaske den Apparat ophiewen oder verursaache kënnen ze wackelen.

Regel 3: Nee Referenz Layer Gap

Et gi Vias iwwer den Apparatperimeter.D'Kraaftnetz gi fir lokal Ofkupplung ofgebrach an dann erof op d'Muechtfliger, déi dacks multiple Vias ubidden fir d'Induktioun ze minimiséieren an d'Stroumtransportkapazitéit ze verbesseren, während de Kontrollbus op de banneschten Plang ka sinn.All dës Zersetzung schlussendlech komplett no beim Apparat ageklemmt ginn.

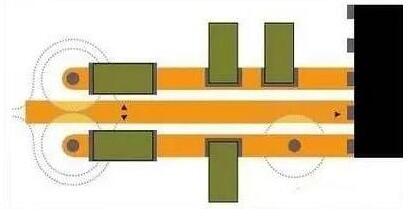

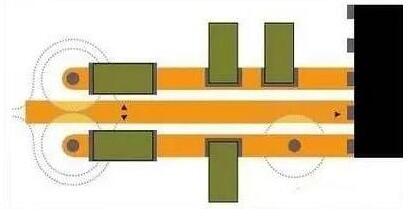

Jiddereng vun dësen vias schaaft eng Ausgrenzung Zone op der bannenzeg Buedem Fliger déi méi grouss ass wéi den Duerchmiesser vun der via selwer, suergt Fabrikatioun Spillraum.Dës Ausgrenzungszonen kënnen einfach Ënnerbriechungen am Retourwee verursaachen.Weider komplizéiert d'Situatioun ass d'Tatsaach, datt e puer Vias no beienee sinn a Buedemplanegruben bilden, déi onsichtbar sinn fir den Top-Niveau CAD Vue.Figur 2. Buedem Fliger Voids fir zwee Muecht Fliger vias kann iwwerlappende halen aus Beräicher schafen an Ënnerbriechungen op de Retour Wee schafen.De Reflow kann nëmmen ëmgeleet ginn fir dat verbuedent Gebitt vum Buedemplang ze ëmgoen, wat zu engem gemeinsame Emissiounsinduktiounsweeproblem resultéiert.

Aacht Regele fir Iech ze hëllefen RF PCB Circuit Parasitics ze reduzéieren

Figur 2: D'Erhaalung Beräicher vun der Äerd Fligeren ronderëm de vias kann iwwerlappt, forcéiert de Retour Flux ewech vum Signal Wee.Och wann et keng Iwwerlappung ass, schaaft d'No-Go-Zone eng Rattebissimpedanzdiskontinuitéit am Buedemplang Souguer "frëndlech" Buedem vias bréngen d'assoziéiert Metal Pads op de Minimum Dimensiounen néideg vun der

gedréckte Circuit Verwaltungsrot Fabrikatioun Prozess.Vias ganz no bei Signal Spure kann Erosioun Erfahrung wéi wann den Top-Niveau Buedem Void vun enger Rat gebass gouf.Figur 2 ass e schemateschen Diagramm vun engem Ratbitt.

Zanter der Exklusioun Zone gëtt automatesch vun der CAD Software generéiert, a vias sinn oft op de System Verwaltungsrot benotzt, et gëtt bal ëmmer e puer Retour Wee Ënnerbriechungen während der fréi Layout Prozess ginn.Tracéiert all Héichgeschwindegkeetslinn wärend der Layoutevaluatioun a kontrolléiert déi assoziéiert Reflowschichten fir Ënnerbriechungen ze vermeiden.Et ass eng gutt Iddi all Vias ze placéieren, déi Grondfligerinterferenz an all Gebitt méi no beim Top-Niveau-Buedemstand kreéieren kënnen.

Regel 4: Halen Differenziell Linnen Differenziell De Retourwee ass kritesch fir d'Signallinnleistung a soll als Deel vum Signalwee ugesi ginn.Zur selwechter Zäit sinn Differentialpaaren normalerweis net enk gekoppelt, an de Retourfluss kann duerch benodeeleg Schichten fléien.Béid Retouren mussen duerch gläich elektresch Weeër geleet ginn.

Proximitéit an Deele Design Aschränkungen halen de Retourfloss op der selwechter Schicht och wann déi zwou Linnen vum Differentialpaar net enk gekoppelt sinn.Fir wierklech spurious Signaler niddereg ze halen, ass besser Matching erfuerderlech.All geplangte Strukturen wéi Ausschnëtter fir Buedempläng ënner Differentialkomponenten solle symmetresch sinn.Och passend Längt kënne Probleemer mat Squiggles an de Signalspuren kreéieren.Reflow verursaacht keng gewellte Probleemer.D'Längtmatchung vun enger Differentiallinn soll an deenen aneren Differentiallinnen reflektéiert ginn.

Regel 5: Keng Auer oder Kontrolllinnen no bei RF Signallinnen Auer- a Kontrolllinnen kënnen heiansdo als onbedeitend Noperen gesi ginn, well se mat nidderegen Geschwindegkeete funktionnéieren, och no bei DC.Wéi och ëmmer, seng Schalteigenschaften si bal Quadratwellen, déi eenzegaarteg Téin op komesch harmonesch Frequenzen produzéieren.D'fundamental Frequenz vun der Emissiounsenergie vun der Quadratwelle ass egal, awer seng scharf Kanten kënnen.Am digitale System Design kann den Eckfrequenz déi héchst Frequenzharmonesch schätzen déi berücksichtegt muss ginn.D'Berechnungsmethod ass: Fknee = 0,5 / Tr, wou Tr d'Steigerzäit ass.Notéiert datt et d'Steigerzäit ass, net d'Signalfrequenz.Wéi och ëmmer, scharf-kantéiert Quadratwellen hunn och staark méi héich-Uerdnung komesch Harmonie, déi nëmmen op der falscher Frequenz falen an op d'RF-Linn koppelen, wat strikt Iwwerdroungsmask Ufuerderunge verletzen.

Auer a Kontrolllinne solle vun RF Signallinnen isoléiert ginn duerch eng intern Buedemfläch oder Top-Level Buedempour.Wann d'Buedemisolatioun net benotzt ka ginn, sollten d'Spuere sou geréckelt ginn datt se an de richtege Wénkel kräizen.Well déi magnetesch Fluxlinnen, déi vun der Auer oder Kontrolllinnen ausgestraalt ginn, Stralungskolonnekonturen ronderëm d'Stréimunge vun den Interfererlinnen bilden, wäerte se keng Stréim an den Empfängerlinnen generéieren.D'Verlängerung vun der Opstiegszäit reduzéiert net nëmmen d'Eckfrequenz, awer hëlleft och d'Interferenz vun den Interferen ze reduzéieren, awer d'Auer oder d'Kontrolllinne kënnen och als Empfängerlinnen handelen.D'Empfängerlinn funktionnéiert nach ëmmer als Conduit fir falsch Signaler an den Apparat.

Regel 6: Benotzt Buedem fir High-Speed-Linnen ze isoléieren Mikrostrips a Striplines si meeschtens un ugrenzend Buedemfläche gekoppelt.E puer Fluxlinnen entstinn ëmmer nach horizontal a schléissen niewendend Spuren of.En Toun op enger Héich-Vitesse Linn oder Differenzial Pair terminéiert op déi nächst Spure, mee Buedem Perfusioun op der Signal Layer schaaft eng niddereg impedance Enn Punkt fir de Flux Linn, befreit bascht Spure vun Téin.

Cluster vu Spuren, déi vun enger Auerverdeelung oder Synthesizer-Apparat geréckelt ginn, fir déiselwecht Frequenz ze droen, kënnen niewentenee lafen, well den Interferer-Toun schonn op der Empfängerlinn präsent ass.Wéi och ëmmer, déi gruppéiert Linnen wäerte sech schlussendlech ausbreeden.Wann d'Verbreedung, soll Buedem Iwwerschwemmung tëscht dem dispersing Linnen a vias ginn, wou et ufänkt ze verdeelen, sou datt d'induzéiert Retour laanscht den nominalen Retour Wee zréck fléisst.An der Figur 3 erlaben Vias um Enn vun de Buedeminselen den induzéierte Stroum op d'Referenzfläch.D'Distanz tëscht anere vias um Buedem Perfusioun soll net een Zéngtel vun enger Wellelängt däerfte fir ze garantéieren datt de Buedem net eng Resonanzstruktur gëtt.

Aacht Regele fir Iech ze hëllefen RF ze reduzéieren

PCB Circuit Parasitics

Figur 3: Top-Niveau Buedem Vias, wou differenziell Spure verspreet sinn, bidden Flow Weeër fir Retour Flux

Regel 7: Gitt net RF Linnen op lauter Kraaftfliger Den Toun geet an d'Muechtfliger an et verbreet sech iwwerall.Wann spurious Téin Energieversuergung, Puffer, Mixer, Attenuatoren, an Oszilléierer erakommen, kënne se d'Stéierungsfrequenz moduléieren.Och wann d'Kraaft de Board erreecht, ass et nach net komplett eidel ginn fir d'RF Circuit ze féieren.Beliichtung vun RF Linnen ze Muecht Fligeren, besonnesch ongefiltert genéissen, soll miniméiert ginn.

Grouss Kraaftfliger niewent dem Buedem kreéieren qualitativ héichwäerteg embedded Kondensatoren déi parasitär Signaler ofschwächen an an digitale Kommunikatiounssystemer an e puer RF Systemer benotzt ginn.Eng aner Approche ass miniméiert Kraaftfliger ze benotzen, heiansdo méi wéi Fettspuren wéi Schichten, sou datt et méi einfach ass fir RF Linnen Kraaftfliger komplett ze vermeiden.Béid Approche si méiglech, awer déi schlëmmste Charakteristike vun deenen zwee däerfen net kombinéiert ginn, dat ass e klenge Kraaftfliger ze benotzen an d'RF Linnen uewen ze routen.

Regel 8: Halt d'Ofkopplung no beim Apparat Net nëmmen d'Entkupplung hëlleft e falsche Geräischer aus dem Apparat ze halen, et hëlleft och Téin ze eliminéieren, déi am Apparat generéiert ginn, aus der Kopplung op d'Kraaftfliger.Wat méi no den Ofkupplungskondensatoren un d'Aarbechtsschaltung sinn, wat méi héich d'Effizienz ass.Lokal Ofkupplung gëtt manner gestéiert duerch parasitär Impedanze vu Circuitboardspuren, a méi kuerz Spuren ënnerstëtzen méi kleng Antennen, reduzéieren onerwënscht Tonal Emissiounen.Capacitor Placement kombinéiert déi héchste Self-Resonanz Frequenz, normalerweis de klengste Wäert, klengste Fall Gréisst, noosten dem Apparat, an der grouss de capacitor, der méi wäit vum Apparat.Bei RF Frequenzen kreéieren d'Kondensatoren op der Récksäit vum Board parasitäre Induktanzen vum via String-zu-Buedem Wee, verléiere vill vum Geräischer Dämpfungsvirdeel.

Zesummefaassung Andeems Dir de Board Layout evaluéiert, kënne mir Strukturen entdecken déi falsch RF Téin iwwerdroen oder kréien.Trace all Linn, identifizéieren bewosst seng Retour Wee, sécherstellen, datt et parallel zu der Linn lafen kann, a virun allem d'Iwwergäng grëndlech kontrolléieren.Isoléiert och potenziell Interferenzquellen vum Empfänger.No e puer einfachen an intuitiv Reegele fir spurious Signaler ze reduzéieren kann d'Produktverëffentlechung beschleunegen an Debug Käschten reduzéieren.

English en

English en