RF PCB ボード スプリアス信号を低減するレイアウトには、RF エンジニアの創造性が必要です。これら 8 つのルールを念頭に置くと、市場投入までの時間を短縮できるだけでなく、作業スケジュールの予測可能性も高まります。

ルール 1: グランド ビアはグランド基準面スイッチに配置する必要があります 配線されたラインを流れるすべての電流は等しいリターンを持ちます。多くの結合方法がありますが、戻りの流れは通常、隣接するグランド プレーンまたは信号線と平行に配置されたグランドを通って流れます。リファレンス層が継続すると、すべての結合は伝送線路に限定され、すべてが完全に正常に動作します。ただし、信号ルーティングが最上層から内部層または最下層に切り替えられた場合、戻りフローにもパスを取得する必要があります。

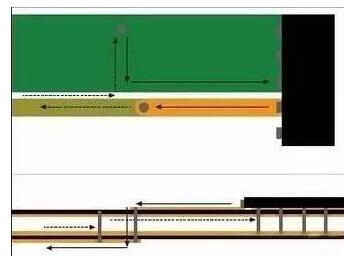

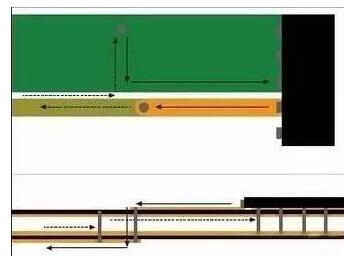

図 1 は一例です。トップレベルの信号線電流の直下にはリターンフローがあります。最下層に移動すると、リフローは近くのビアを通過します。ただし、近くにリフロー用のビアがない場合、リフローは最も近い利用可能なグランド ビアを経由します。距離が長くなると電流ループが形成され、インダクタが形成されます。この望ましくない電流パスのオフセットが別のラインと交差する場合、干渉はより深刻になります。この電流ループは、実際にはアンテナを形成することに相当します。

RF PCB 回路の寄生成分を削減するための 8 つのルール

図 1: 信号電流はデバイスのピンからビアを通って下位層に流れます。リフローは、別のリファレンス層に変更するために最も近いビアに強制される前に、信号の下にあります。

図 1: 信号電流はデバイスのピンからビアを通って下位層に流れます。リフローは、別のリファレンス層に変更するために最も近いビアに強制される前に、信号の下にあります。 グランド リファレンスが最善の戦略ですが、高速回線が内部レイヤーに配置される場合もあります。グランド基準面を上下に配置するのは非常に難しく、半導体メーカーはピンに制約があり、電源線を高速線の隣に配置する場合があります。DC 結合されていない層またはネット間で基準電流を切り替える必要がある場合は、スイッチ ポイントの隣にデカップリング コンデンサを配置する必要があります。

ルール 2: デバイスのパッドを最上層のグランドに接続する 多くのデバイスでは、デバイス パッケージの底部にサーマル グランド パッドが使用されています。RF デバイスでは、これらは通常電気的なアースであり、隣接するパッド ポイントには一連のアース ビアがあります。デバイスのパッドは、グランド ピンに直接接続したり、最上層のグランドを介して銅を流し込んだりすることができます。複数のパスがある場合、戻りの流れはパスのインピーダンスに比例して分割されます。パッドを介したグランド接続は、ピン グランドよりも短く、インピーダンスが低くなります。

ボードとデバイスのパッド間の電気接続が良好であることが重要です。組み立て中に、回路基板のビア アレイ内の未充填のビアによってデバイスからはんだペーストが引き出され、ボイドが残る場合もあります。スルーホールを埋めることは、はんだ付けを所定の位置に保つための良い方法です。評価中は、はんだマスク層を開いて、デバイスの下の基板グランドにはんだマスクがないことも確認します。これは、はんだマスクによってデバイスが持ち上げられたり、ぐらついたりする可能性があるためです。

ルール 3: 参照レイヤー ギャップなし

デバイスの周囲全体にビアがあります。電源ネットはローカル デカップリングのために分割され、その後電源プレーンに至り、多くの場合、インダクタンスを最小限に抑えて通電容量を向上させるために複数のビアが提供されますが、制御バスは内部プレーンにまで到達することができます。この分解はすべて、最終的にデバイスの近くに完全に固定されます。

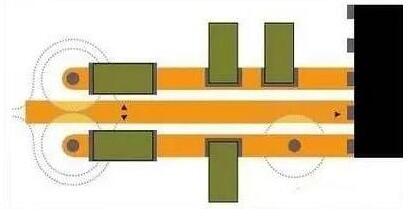

これらの各ビアは、ビア自体の直径よりも大きい内部グランド プレーン上に除外ゾーンを作成し、製造上のクリアランスを提供します。これらの立ち入り禁止ゾーンにより、復路が簡単に中断される可能性があります。状況をさらに複雑にしているのは、一部のビアが互いに近接しており、トップレベルの CAD ビューでは見えないグランド プレーン トレンチを形成しているという事実です。図 2. 2 つの電源プレーン ビアのグランド プレーンのボイドにより、オーバーラップする禁止エリアが作成され、リターン パスに中断が生じる可能性があります。リフローは、グランドプレーンの禁止領域をバイパスするためにのみ迂回することができ、その結果、共通の放射誘導経路の問題が発生します。

RF PCB 回路の寄生成分を削減するための 8 つのルール

図 2: ビア周囲のグランド プレーンの立ち入り禁止領域が重なり、リターン フローが信号パスから遠ざかる可能性があります。たとえ重なりがなかったとしても、立ち入り禁止ゾーンにより、グランドプレーンにネズミの咬傷によるインピーダンスの不連続が生じます。 「フレンドリーな」グランドビアであっても、関連する金属パッドを必要な最小寸法にします。

プリント基板の製造 プロセス。信号トレースに非常に近いビアでは、最上層の地面の空隙がネズミに噛み切られたかのように浸食が発生する可能性があります。図2はネズミの咬傷の模式図である。

除外ゾーンは CAD ソフトウェアによって自動的に生成され、ビアはシステム ボード上で頻繁に使用されるため、初期のレイアウト プロセスではほとんどの場合、リターン パスの中断が発生します。レイアウト評価中に各高速ラインをトレースし、中断を避けるために関連するリフロー層をチェックします。グランド プレーン干渉を引き起こす可能性のあるすべてのビアを、最上位のグランド ボイドに近い領域に配置することをお勧めします。

ルール 4: 差動ラインの差動を維持する リターンパスは信号線のパフォーマンスにとって重要であり、信号パスの一部として考慮する必要があります。同時に、差動ペアは通常、緊密に結合されていないため、戻りの流れが隣接する層を通って流れる可能性があります。両方のリターンは等しい電気経路を介して配線する必要があります。

近接性と共有設計の制約により、差動ペアの 2 つのラインが緊密に結合されていない場合でも、戻りの流れが同じ層に維持されます。スプリアス信号を実際に低く抑えるには、より適切なマッチングが必要です。差動コンポーネントの下のグランドプレーンのカットアウトなど、計画された構造はすべて対称である必要があります。同様に、長さを一致させると、信号トレースの波線に関する問題が発生する可能性があります。リフローでは波打ちの問題は発生しません。1 つの差動線の長さの一致は、他の差動線にも反映される必要があります。

ルール 5: RF 信号線の近くにクロック線や制御線を配置しない クロックおよび制御ラインは、DC に近い低速で動作するため、重要ではない隣接ラインとしてみなされる場合があります。ただし、そのスイッチング特性はほぼ方形波であり、奇数次の高調波周波数で独特のトーンを生成します。方形波の放射エネルギーの基本周波数は重要ではありませんが、その鋭いエッジは重要です。デジタル システム設計では、コーナー周波数により、考慮する必要がある最高周波数高調波を推定できます。計算方法は、Fknee=0.5/Tr です。ここで、Tr は立ち上がり時間です。これは信号周波数ではなく立ち上がり時間であることに注意してください。ただし、エッジの鋭い方形波には強い高次の奇数高調波も含まれており、誤った周波数でドロップして RF ラインに結合する可能性があり、厳密な送信マスク要件に違反します。

クロックおよび制御ラインは、内部グランド プレーンまたはトップレベル グランド ポアによって RF 信号ラインから絶縁する必要があります。接地絶縁を使用できない場合は、配線が直角に交差するように配線する必要があります。クロック線または制御線によって放出される磁束線は、干渉線の電流の周りに放射状の柱の輪郭を形成するため、受信線には電流が生成されません。立ち上がり時間を遅くすると、コーナー周波数が低下するだけでなく、干渉源からの干渉も軽減されます。また、クロックまたは制御ラインが受信ラインとして機能することもあります。受信回線は依然として、デバイスへのスプリアス信号の導管として機能します。

ルール 6: グランドを使用して高速回線を絶縁する マイクロストリップとストリップラインは、ほとんどの場合、隣接するグランド プレーンに結合されます。一部の磁束線は依然として水平方向に放射され、隣接するトレースを終了します。1 つの高速ラインまたは差動ペアのトーンは次のトレースで終端しますが、信号層のグランド灌流により磁束線のインピーダンスが低い終端点が作成され、隣接するトレースがトーンから解放されます。

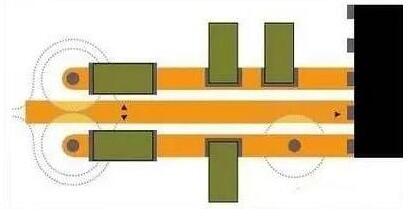

同じ周波数を伝送するためにクロック分配またはシンセサイザー デバイスによってルーティングされたトレースのクラスターは、受信回線に干渉トーンがすでに存在しているため、互いに隣接して実行される可能性があります。しかし、グループ化されたラインは最終的には広がります。分散する場合、誘導されたリターンが公称リターンパスに沿って逆流するように、分散ラインと分散が始まるビアの間にグランドフラッディングを設ける必要があります。図 3 では、グランド アイランドの端にあるビアにより、誘導電流が基準面に流れることができます。グランドが共振構造にならないように、グランド灌流上の他のビア間の間隔は波長の 10 分の 1 を超えてはなりません。

RF を減らすための 8 つのルール

PCB 回路の寄生要素

図 3: 差動配線が散在するトップレベルのグランド ビアは、リターン フローの流路を提供します

ルール 7: ノイズの多い電源プレーン上に RF ラインを配線しない トーンは電源プレーンに入り、あらゆる場所に広がります。スプリアス トーンが電源、バッファ、ミキサ、減衰器、発振器に侵入すると、干渉周波数が変調される可能性があります。同様に、電力がボードに到達しても、RF 回路を駆動するために電力はまだ完全には空になっていません。電源プレーン、特にフィルタされていない電源プレーンへの RF ラインの露出は最小限に抑える必要があります。

グランドに隣接する大きな電源プレーンは、寄生信号を減衰する高品質の埋め込みコンデンサを作成し、デジタル通信システムや一部の RF システムで使用されます。もう 1 つのアプローチは、RF ラインが電源プレーンを完全に回避しやすくなるように、最小化された電源プレーンを使用することです。どちらのアプローチも可能ですが、2 つの最悪の特性を組み合わせてはなりません。これは、小さな電源プレーンを使用し、その上に RF ラインを配線することです。

ルール 8: デバイスの近くでデカップリングを続ける デカップリングは、デバイスからのスプリアス ノイズを防ぐだけでなく、デバイス内で生成されるトーンが電源プレーンに結合するのを防ぐことにも役立ちます。デカップリング コンデンサが動作回路に近づくほど、効率は高くなります。ローカル デカップリングは、回路基板トレースの寄生インピーダンスによって妨げられることが少なく、短いトレースがより小さなアンテナをサポートし、不要なトーン放射を低減します。コンデンサの配置は、最高の自己共振周波数、通常は最小値、最小のケースサイズを組み合わせてデバイスに最も近く、コンデンサが大きくなるほどデバイスから遠ざかります。RF 周波数では、基板裏面のコンデンサがビアストリングからグランドへの経路の寄生インダクタンスを生成し、ノイズ減衰の利点の多くが失われます。

要約する 基板レイアウトを評価することで、スプリアス RF トーンを送信または受信する可能性のある構造を発見できます。各ラインをトレースし、その戻りパスを意識的に特定し、ラインと平行に実行できることを確認し、特にトランジションを徹底的にチェックします。また、潜在的な干渉源を受信機から隔離してください。いくつかのシンプルで直観的なルールに従ってスプリアス信号を削減すると、製品のリリースを加速し、デバッグ コストを削減できます。

English jp

English jp