Placa PCB de RF layout para reduzir sinais espúrios requer a criatividade do engenheiro de RF.Manter essas oito regras em mente não apenas ajudará a acelerar o tempo de colocação no mercado, mas também aumentará a previsibilidade do seu cronograma de trabalho.

Regra 1: As vias de aterramento devem estar localizadas na chave do plano de referência de aterramento Todas as correntes que fluem através da linha roteada têm retorno igual.Existem muitas estratégias de acoplamento, mas o fluxo de retorno geralmente flui através de planos de aterramento adjacentes ou aterramentos colocados em paralelo com as linhas de sinal.À medida que a camada de referência continua, todo o acoplamento é limitado à linha de transmissão e tudo funciona perfeitamente bem.No entanto, se o roteamento do sinal for trocado da camada superior para a camada interna ou inferior, o fluxo de retorno também deve obter um caminho.

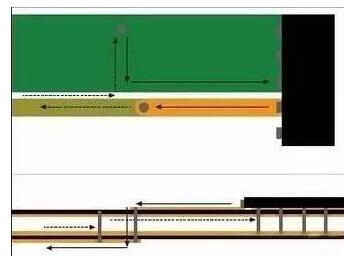

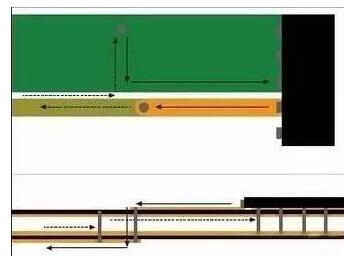

A Figura 1 é um exemplo.Imediatamente abaixo da corrente de linha de sinal de nível superior está o fluxo de retorno.Quando se transfere para a camada inferior, o refluxo passa por vias próximas.No entanto, se não houver vias de refluxo próximas, o refluxo passa pela via terrestre disponível mais próxima.Distâncias maiores criam loops de corrente, formando indutores.Se esse deslocamento de caminho de corrente indesejado cruzar outra linha, a interferência será mais severa.Este loop de corrente é realmente equivalente a formar uma antena!

Oito regras para ajudá-lo a reduzir os parasitas do circuito RF PCB

Figura 1: A corrente de sinal flui dos pinos do dispositivo através das vias para as camadas inferiores.O refluxo está sob o sinal antes de ser forçado para a via mais próxima para mudar para uma camada de referência diferente

Figura 1: A corrente de sinal flui dos pinos do dispositivo através das vias para as camadas inferiores.O refluxo está sob o sinal antes de ser forçado para a via mais próxima para mudar para uma camada de referência diferente O referenciamento de solo é a melhor estratégia, mas as linhas de alta velocidade às vezes podem ser colocadas em camadas internas.Colocar planos de referência de solo acima e abaixo é muito difícil, e os fabricantes de semicondutores podem ter restrições de pinos e colocar linhas de energia próximas a linhas de alta velocidade.Se a corrente de referência precisar ser comutada entre camadas ou redes que não são acopladas em CC, os capacitores de desacoplamento devem ser colocados próximos ao ponto de comutação.

Regra 2: Conecte o pad do dispositivo ao solo da camada superior Muitos dispositivos usam um bloco de aterramento térmico na parte inferior da embalagem do dispositivo.Em dispositivos de RF, estes são tipicamente aterramentos elétricos e os pontos de pad adjacentes possuem uma matriz de vias de aterramento.O pad do dispositivo pode ser conectado diretamente ao pino de aterramento e conectado a qualquer vazamento de cobre através do aterramento da camada superior.Se houver vários caminhos, o fluxo de retorno é dividido proporcionalmente à impedância do caminho.A conexão de aterramento através do pad tem um caminho de impedância menor e mais curto do que o pino de aterramento.

Uma boa conexão elétrica entre a placa e os pads do dispositivo é crítica.Durante a montagem, vias não preenchidas em uma placa de circuito via array também podem extrair pasta de solda do dispositivo, deixando vazios.Preencher os orifícios é uma boa maneira de manter a solda no lugar.Durante a avaliação, abra também a camada de máscara de solda para verificar se não há máscara de solda no chão da placa abaixo do dispositivo, pois a máscara de solda pode levantar o dispositivo ou fazer com que ele balance.

Regra 3: Nenhuma lacuna da camada de referência

Existem vias em todo o perímetro do dispositivo.As redes de energia são divididas para desacoplamento local e depois para o plano de energia, geralmente fornecendo várias vias para minimizar a indutância e melhorar a capacidade de transporte de corrente, enquanto o barramento de controle pode estar no plano interno.Toda essa decomposição acaba ficando totalmente grampeada próximo ao aparelho.

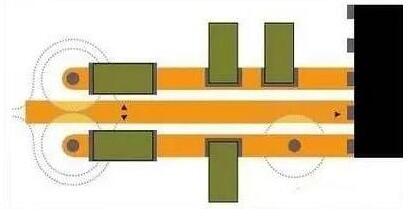

Cada uma dessas vias cria uma zona de exclusão no plano de aterramento interno que é maior que o diâmetro da própria via, fornecendo folga de fabricação.Essas zonas de exclusão podem facilmente causar interrupções no caminho de retorno.Para complicar ainda mais a situação, algumas vias estão próximas umas das outras e formam trincheiras de plano de terra que são invisíveis para a visualização CAD de nível superior.Figura 2. Vazios no plano de aterramento para duas vias do plano de energia podem criar áreas de exclusão sobrepostas e criar interrupções no caminho de retorno.O refluxo só pode ser desviado para contornar a área proibida do plano de aterramento, resultando no problema do caminho de indução de emissão comum.

Oito regras para ajudá-lo a reduzir os parasitas do circuito RF PCB

Figura 2: As áreas de bloqueio dos planos de terra ao redor das vias podem se sobrepor, forçando o fluxo de retorno para longe do caminho do sinal.Mesmo que não haja sobreposição, a zona proibida cria uma descontinuidade de impedância de mordida de rato no plano de aterramento Mesmo as vias de aterramento "amigáveis" trazem as almofadas de metal associadas às dimensões mínimas exigidas pelo

fabricação de placa de circuito impresso processo.Vias muito próximas a traços de sinal podem sofrer erosão como se o vazio do solo de nível superior tivesse sido mordido por um rato.A Figura 2 é um diagrama esquemático de uma mordida de rato.

Como a zona de exclusão é gerada automaticamente pelo software CAD e as vias são frequentemente usadas na placa do sistema, quase sempre haverá algumas interrupções no caminho de retorno durante o processo inicial de layout.Rastreie cada linha de alta velocidade durante a avaliação do layout e verifique as camadas de refluxo associadas para evitar interrupções.É uma boa ideia colocar todas as vias que podem criar interferência no plano de aterramento em qualquer área mais próxima do vazio de aterramento de nível superior.

Regra 4: Mantenha o Diferencial das Linhas Diferenciais O caminho de retorno é crítico para sinalizar o desempenho da linha e deve ser considerado parte do caminho do sinal.Ao mesmo tempo, os pares diferenciais geralmente não são fortemente acoplados e o fluxo de retorno pode fluir através de camadas adjacentes.Ambos os retornos devem ser roteados através de caminhos elétricos iguais.

As restrições de projeto de proximidade e compartilhamento mantêm o fluxo de retorno na mesma camada, mesmo quando as duas linhas do par diferencial não estão fortemente acopladas.Para realmente manter os sinais espúrios baixos, é necessária uma melhor correspondência.Quaisquer estruturas planejadas, como recortes para planos de terra sob componentes diferenciais, devem ser simétricas.Da mesma forma, comprimentos correspondentes podem criar problemas com rabiscos nos traços de sinal.O refluxo não causa problemas de ondulação.A correspondência de comprimento de uma linha diferencial deve ser refletida nas outras linhas diferenciais.

Regra 5: Sem clock ou linhas de controle perto das linhas de sinal de RF Às vezes, as linhas de clock e controle podem ser vistas como vizinhas insignificantes porque operam em baixas velocidades, mesmo próximas de CC.No entanto, suas características de comutação são quase de onda quadrada, produzindo tons únicos em frequências harmônicas ímpares.A frequência fundamental da energia de emissão da onda quadrada não importa, mas sim suas arestas vivas.No projeto do sistema digital, a frequência de canto pode estimar o harmônico de frequência mais alta que deve ser considerado.O método de cálculo é: Fknee=0,5/Tr, onde Tr é o tempo de subida.Observe que é o tempo de subida, não a frequência do sinal.No entanto, as ondas quadradas de arestas vivas também têm fortes harmônicos ímpares de ordem superior que podem cair apenas na frequência errada e se acoplar à linha de RF, violando os requisitos rígidos da máscara de transmissão.

As linhas de relógio e controle devem ser isoladas das linhas de sinal de RF por um plano de aterramento interno ou vazamento de aterramento de nível superior.Se o isolamento do solo não puder ser usado, os traços devem ser roteados de forma que se cruzem em ângulos retos.Como as linhas de fluxo magnético emitidas pelo relógio ou linhas de controle formarão contornos de colunas radiantes em torno das correntes das linhas interferentes, elas não gerarão correntes nas linhas receptoras.Diminuir o tempo de subida não apenas reduz a frequência de canto, mas também ajuda a reduzir a interferência de interferentes, mas o relógio ou as linhas de controle também podem atuar como linhas receptoras.A linha do receptor ainda atua como um canal para sinais espúrios no dispositivo.

Regra 6: Use o solo para isolar linhas de alta velocidade Microstrips e striplines são geralmente acoplados a planos de terra adjacentes.Algumas linhas de fluxo ainda emanam horizontalmente e terminam traços adjacentes.Um tom em uma linha de alta velocidade ou par diferencial termina no próximo traço, mas a perfusão do solo na camada de sinal cria um ponto de terminação de impedância mais baixa para a linha de fluxo, liberando traços adjacentes de tons.

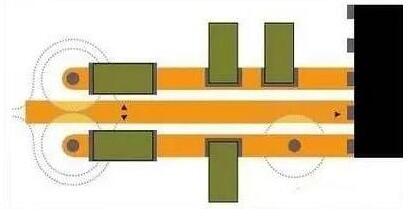

Clusters de traços roteados por uma distribuição de relógio ou dispositivo sintetizador para transportar a mesma frequência podem correr próximos uns dos outros porque o tom interferente já está presente na linha receptora.No entanto, as linhas agrupadas acabarão se espalhando.Ao dispersar, a inundação do solo deve ser fornecida entre as linhas e vias de dispersão onde começa a se dispersar para que o retorno induzido flua de volta ao longo do caminho de retorno nominal.Na Figura 3, as vias nas extremidades das ilhas de aterramento permitem que a corrente induzida flua para o plano de referência.O espaçamento entre outras vias na perfusão do solo não deve exceder um décimo de comprimento de onda para garantir que o solo não se torne uma estrutura ressonante.

Oito regras para ajudá-lo a reduzir a RF

Parasitas do Circuito PCB

Figura 3: As vias de solo de nível superior, onde os traços diferenciais são dispersos, fornecem caminhos de fluxo para o fluxo de retorno

Regra 7: Não roteie linhas de RF em planos de energia ruidosos O tom entra no plano de poder e se espalha por toda parte.Se tons espúrios entrarem em fontes de alimentação, buffers, misturadores, atenuadores e osciladores, eles podem modular a frequência de interferência.Da mesma forma, quando a energia chega à placa, ela ainda não foi completamente esvaziada para acionar o circuito de RF.A exposição de linhas de RF a planos de energia, especialmente planos de energia não filtrados, deve ser minimizada.

Grandes planos de energia adjacentes ao solo criam capacitores embutidos de alta qualidade que atenuam sinais parasitas e são usados em sistemas de comunicação digital e alguns sistemas de RF.Outra abordagem é usar planos de energia minimizados, às vezes mais como traços de gordura do que camadas, de modo que seja mais fácil para as linhas de RF evitar completamente os planos de energia.Ambas as abordagens são possíveis, mas as piores características das duas não devem ser combinadas, que é usar um pequeno plano de potência e rotear as linhas de RF por cima.

Regra 8: Mantenha o desacoplamento próximo ao dispositivo O desacoplamento não apenas ajuda a manter o ruído espúrio fora do dispositivo, como também ajuda a eliminar os tons gerados dentro do dispositivo do acoplamento nos planos de energia.Quanto mais próximos os capacitores de desacoplamento estiverem dos circuitos de trabalho, maior será a eficiência.O desacoplamento local é menos perturbado por impedâncias parasitas de traços de placa de circuito, e traços mais curtos suportam antenas menores, reduzindo emissões tonais indesejadas.A colocação do capacitor combina a frequência auto-ressonante mais alta, geralmente o menor valor, o menor tamanho de caixa, mais próximo do dispositivo e, quanto maior o capacitor, mais longe do dispositivo.Em frequências de RF, os capacitores na parte traseira da placa criam indutâncias parasitas do caminho via string-terra, perdendo muito do benefício de atenuação de ruído.

Resumir Ao avaliar o layout da placa, podemos descobrir estruturas que podem transmitir ou receber tons de RF espúrios.Trace cada linha, identifique conscientemente seu caminho de retorno, certifique-se de que ela pode correr paralelamente à linha e, principalmente, verifique cuidadosamente as transições.Além disso, isole fontes potenciais de interferência do receptor.Seguir algumas regras simples e intuitivas para reduzir sinais espúrios pode acelerar o lançamento do produto e reduzir os custos de depuração.

English pt

English pt